Notes about PCIe prefetchable bar

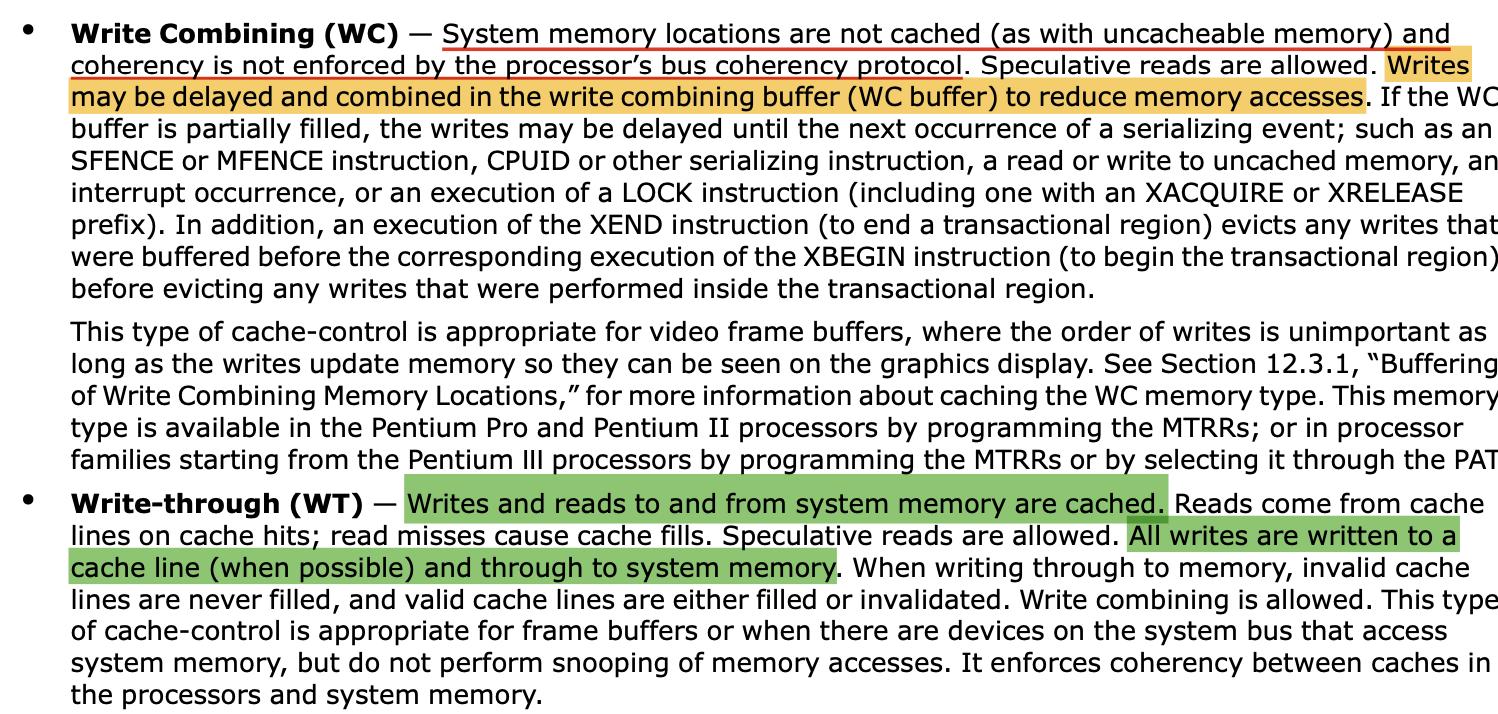

When a base address register is marked as Prefetchable, it means that:the region does not have read side effects (reading from that memory range doesn’t change any state), and it is allowed for the CPU to cache loads from that memory region and read it in bursts (typically cache line sized). Hardware is also allowed to merge repeated stores to the same address into one store of the latest value. If you are using paging and want maximum performance, you should map prefetchable MMIO regions as WT (write-through) instead of UC (uncacheable). On x86, frame buffers are the exception, they should be almost always be mapped WC (write-combining).

参考资料:

- wiki.osdev.org/PCI

- PCIE的prefetchable和nonprefetchable的理解

- Intel SDM Vol3