Notes about AMD IOMMU IRTCache机制

文章目录

本文将mark下AMD IOMMU IRTCache机制的相关notes。

Motivation

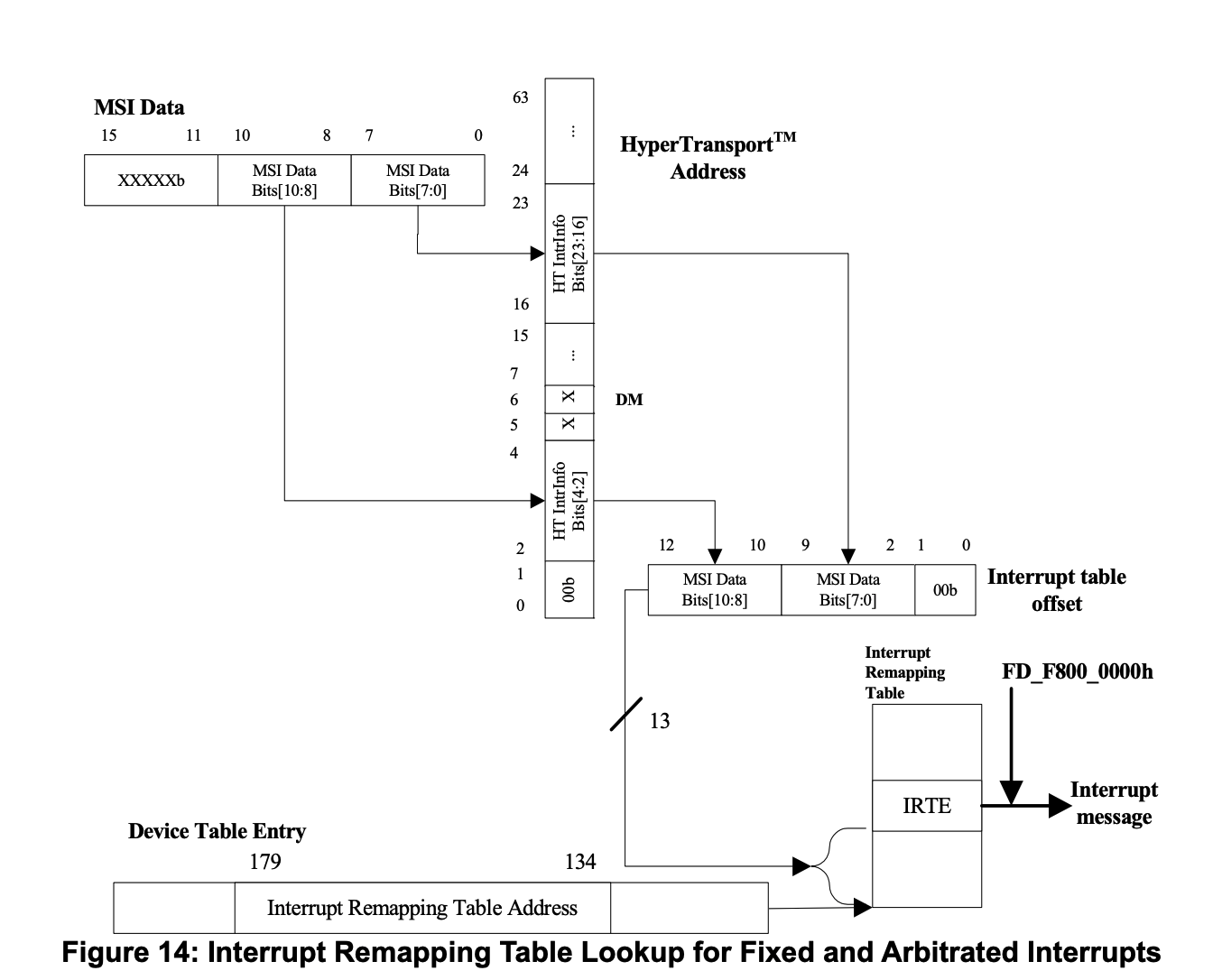

在没有IRTCache机制之前,设备的MSI data到IRTE(Interrupt Remapping Table Entry)的映射,需要硬件从内存中读取Interrupt Remapping Table来获取IRTE。

在引入IRTCache机制之后,IOMMU硬件中就会缓存设备MSI data到IRTE的映射了,这样就可以避免IOMMU硬件从内存中读取IRTE。

How

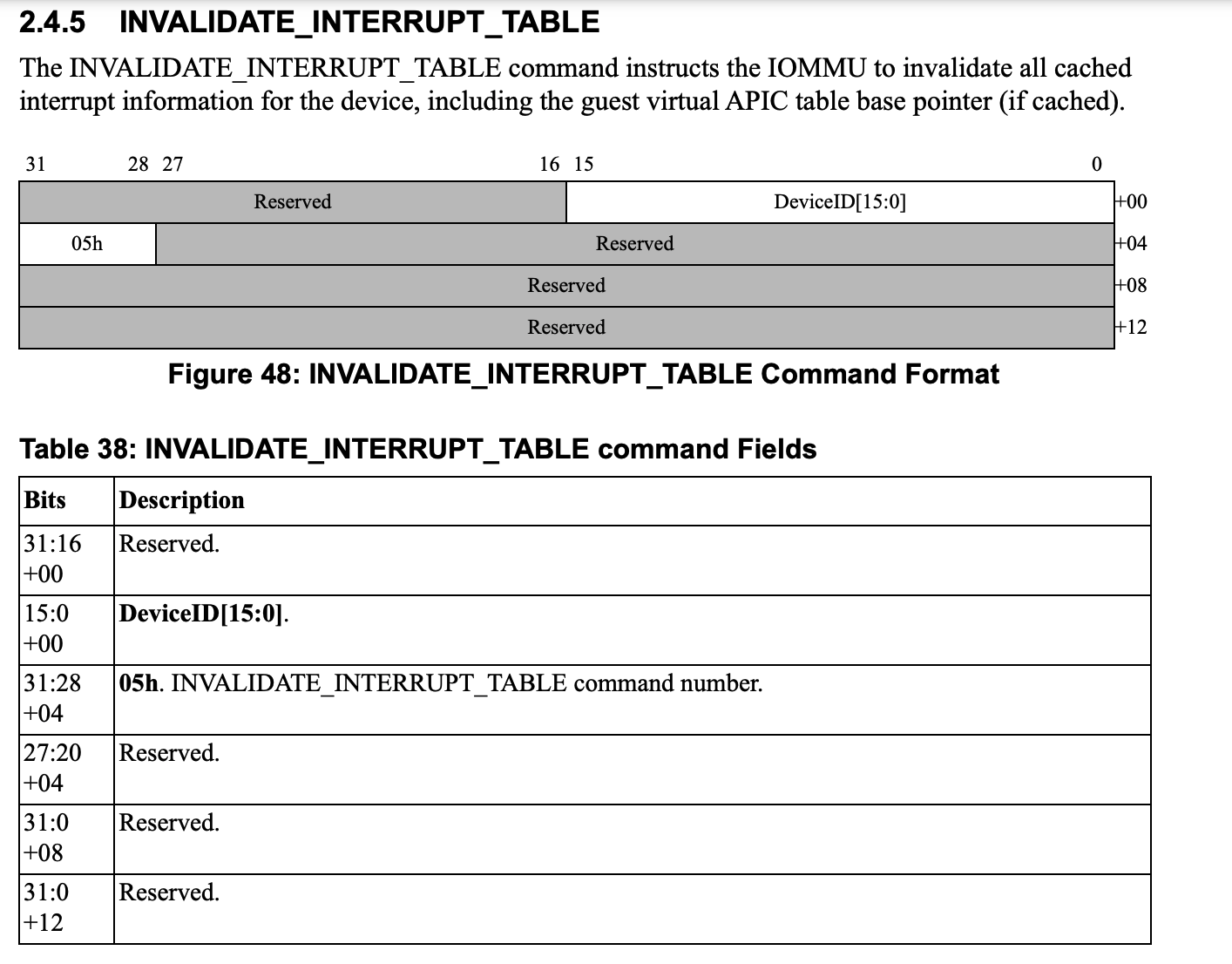

For IOMMU AVIC, the IOMMU driver needs to keep track of vcpu scheduling changes, and updates interrupt remapping table entry (IRTE) accordingly. The IRTE is normally cached by the hardware, which requires the IOMMU driver to issue IOMMU IRT invalidation command and wait for completion everytime it updates the table.

Enabling IOMMU AVIC on a large scale system with lots of vcpus and VFIO pass-through devices running interrupt-intensive workload, it could result in high IRT invalidation rate. In such case, the overhead from IRT invalidation could outweigh the benefit of IRTE caching.

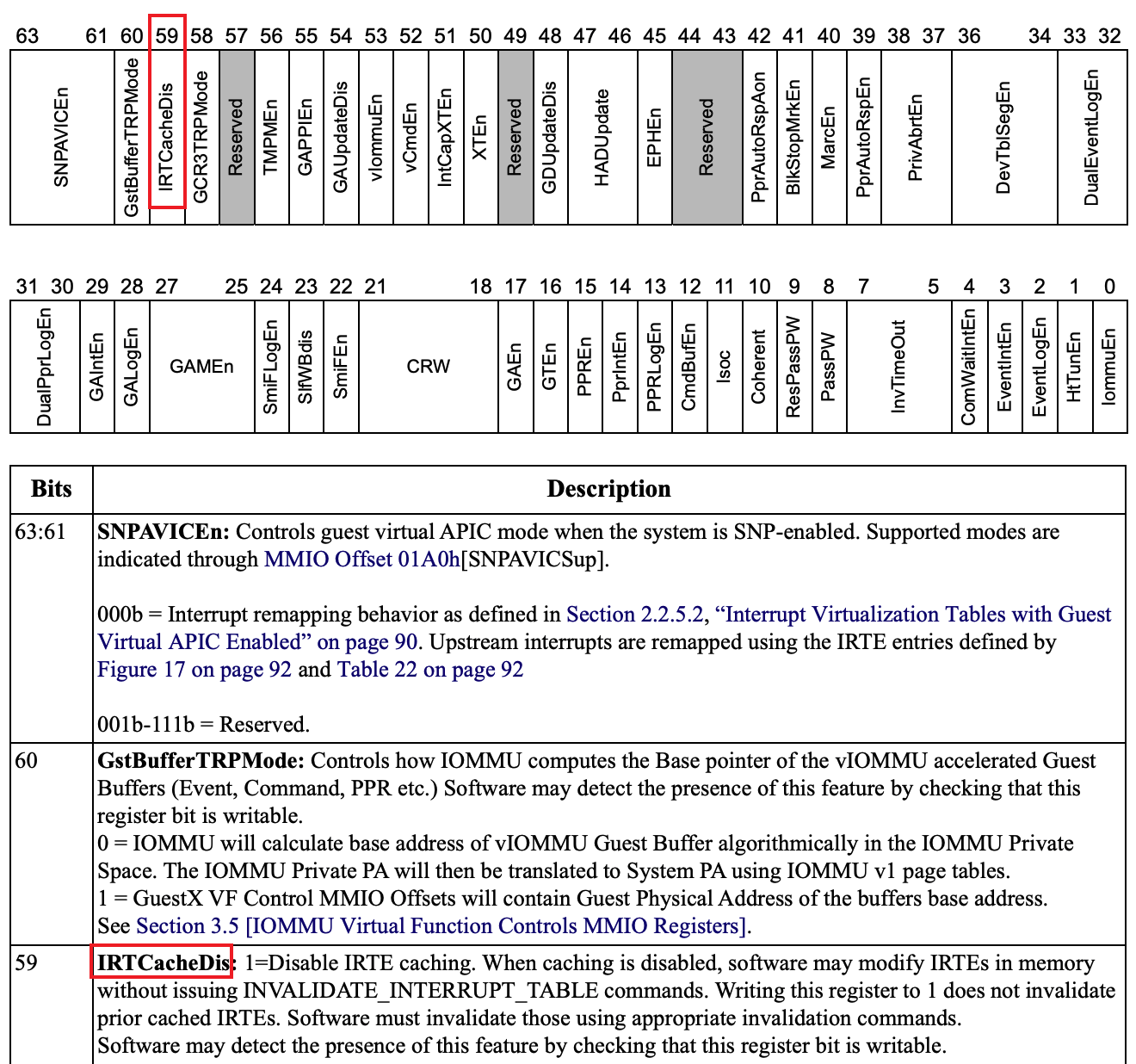

Therefore, introduce a new AMD IOMMU driver option “amd_iommu=irtcachedis” to allow disabling IRTE caching, and avoid the need for IRTE invalidation.

参考资料:

- [PATCH v3 0/5] iommu/amd: AVIC Interrupt Remapping Improvements

- AMD I/O Virtualization Technology (IOMMU) Specification, 48882