Performance Implications of Extended Page Tables on Virtualized x86 Processors

文章目录

Performance Implications of Extended Page Tables on Virtualized x86 Processors

相关资料

作者

| 姓名 | 主页 | 谷歌学术 | dblp |

|---|---|---|---|

| Timothy Merrifield | Timothy Merrifield | Timothy Merrifield | Timothy Merrifield |

| H. Reza Taheri | H. Reza Taheri | H. Reza Taheri |

介绍

本文的主要贡献是表明:如果使用最新的硬件和软件栈(paging structure caches and the L1/L2 data caches),虚拟化环境下TLB miss处理开销实际上是整体TLB miss处理开销的一小部分。

背景

本文的背景知识需要好好阅读,可以学到好多知识。

Native地址映射

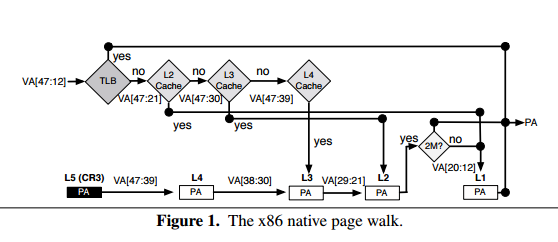

利用page structure caches,页寻址过程如下图。

虚拟化环境下的地址映射

TLB 缓存与页面大小

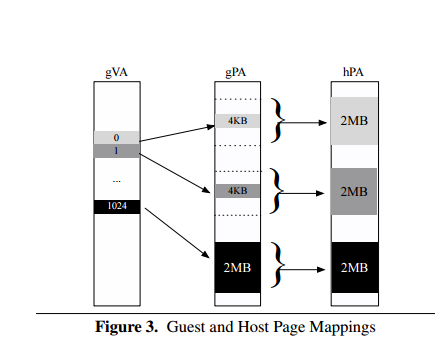

使用大页映射时,可以减少TLB miss,在虚拟化环境中,客户机和主机必须将页面映射到2MB,以允许处理器使用2MB TLB entry。下图显示了这种效果; 页0和页1在客户机中使用小页,页1024在客户机中使用大页。在主机中,客户机占用的内存局域都使用大页。页0和页1显然不能使用2MB的TLB entry,因为页0和页1在物理主机上并不连续。而页1024可以使用2MB TLB entry,因为页1024在gPA和hPA上都使用了大页。

总结

虚拟化对TLB miss的性能影响并不如人们想象的那么严重, 虽然通过EPT最坏的情况看起来过高,但在有较多TLB entry和paging structure caches的现代处理器情况下,Native和EPT的TLB miss 造成的性能损失大大降低。