computer chipset and bus

本文将总结computer chipset与bus的相关内容。不同型号的cpu,chipset可能不同。本文的目的是对这些chipset与bus进行汇总,从而建立计算机内部芯片的拓扑结构。

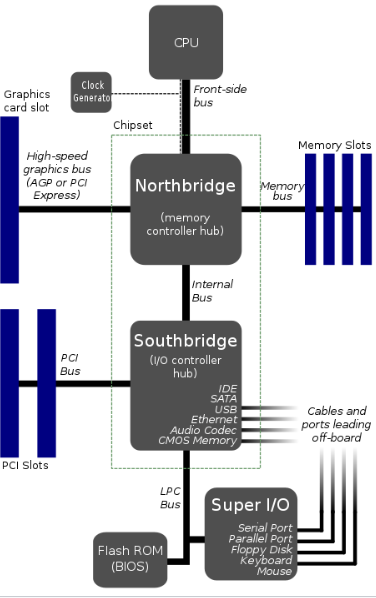

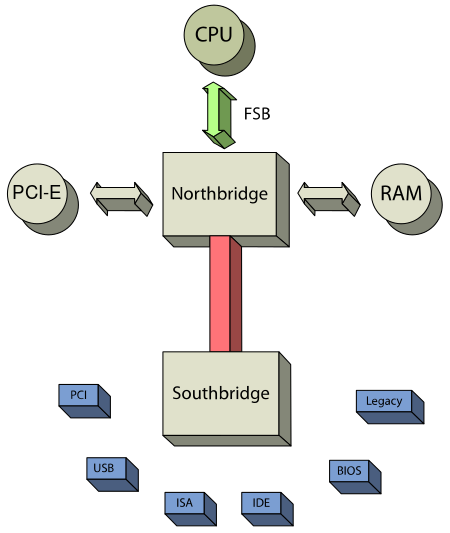

北桥

northbridge,也称为host bridge。On older Intel based PCs, the northbridge was also named external memory controller hub (MCH) or graphics and memory controller hub (GMCH) if equipped with integrated graphics.

https://en.wikipedia.org/wiki/Northbridge_(computing)

南桥

The south bridge chip, also called ICH (I/O Controller Hub) or PCH (Platform Controller Hub) is connected to the north bridge (or the CPU, in the case of current Intel CPUs) and is in charge of controlling I/O devices and on-board devices

https://en.wikipedia.org/wiki/Platform_Controller_Hub

https://www.hardwaresecrets.com/everything-you-need-to-know-about-chipsets/3/

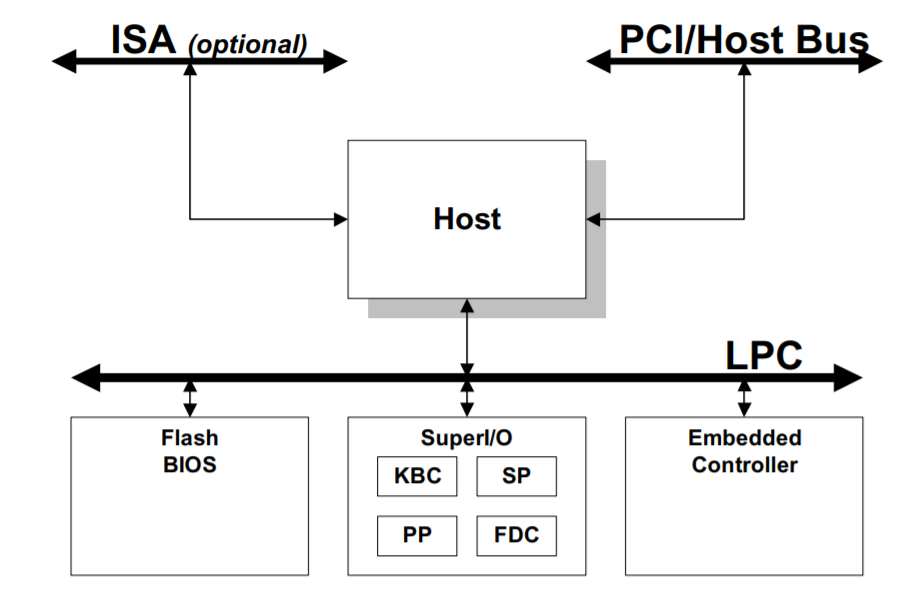

lpc bus

The Low Pin Count (LPC) interface is a low bandwidth bus with up to 33 MHz performance. It is used to connect peripherals around the CPU and to replace the Industry Standard Architecture (ISA) bus which can only run up to 8 MHz.

https://en.wikipedia.org/wiki/Low_Pin_Count

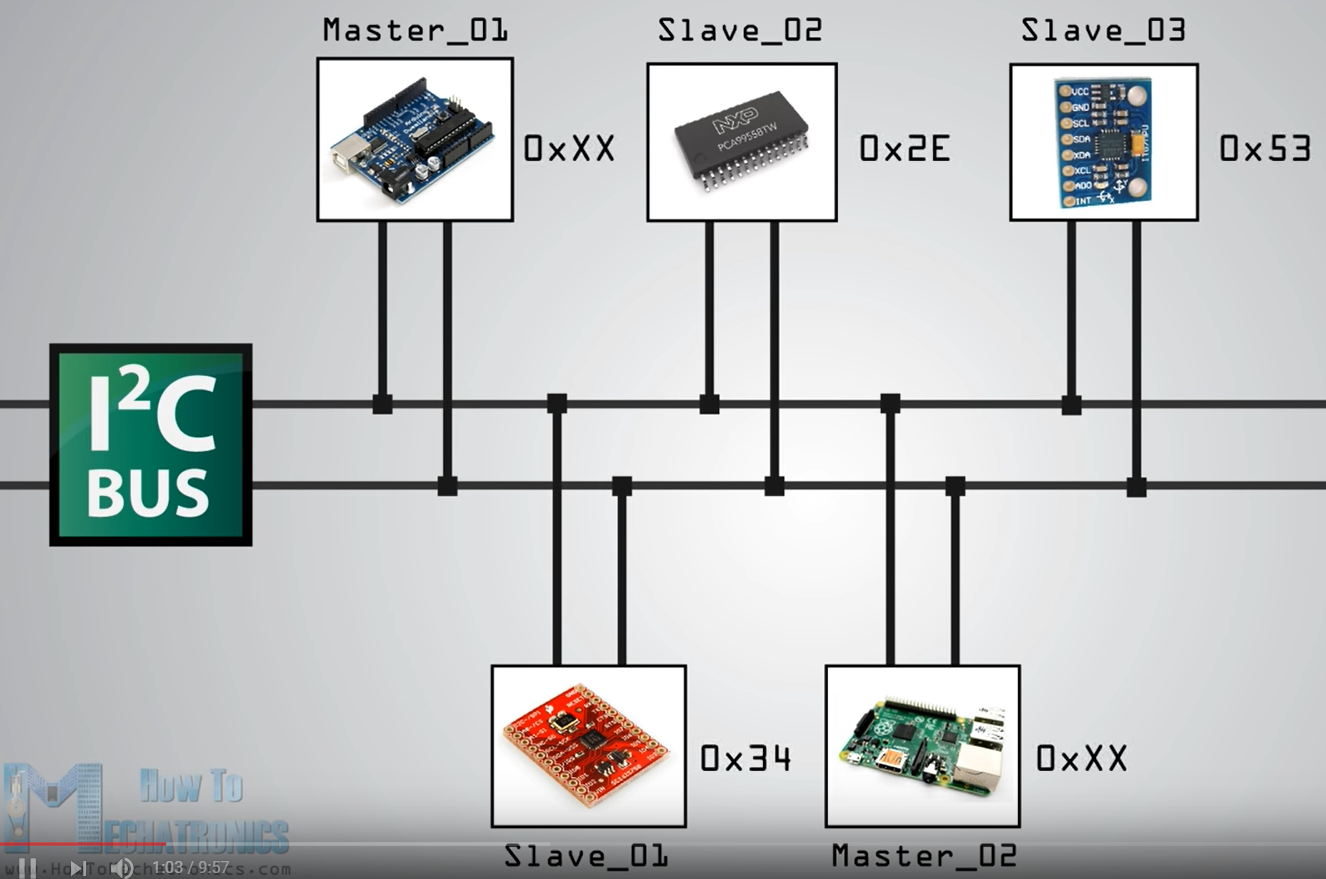

i2c bus

I2C bus is widely used for attaching lower-speed peripheral to processors and microcontrollers in short-distance, intra-board communication.

https://en.wikipedia.org/wiki/I%C2%B2C

https://www.kernel.org/doc/html/v4.14/driver-api/i2c.html

https://www.youtube.com/watch?v=6IAkYpmA1DQ&t=83s

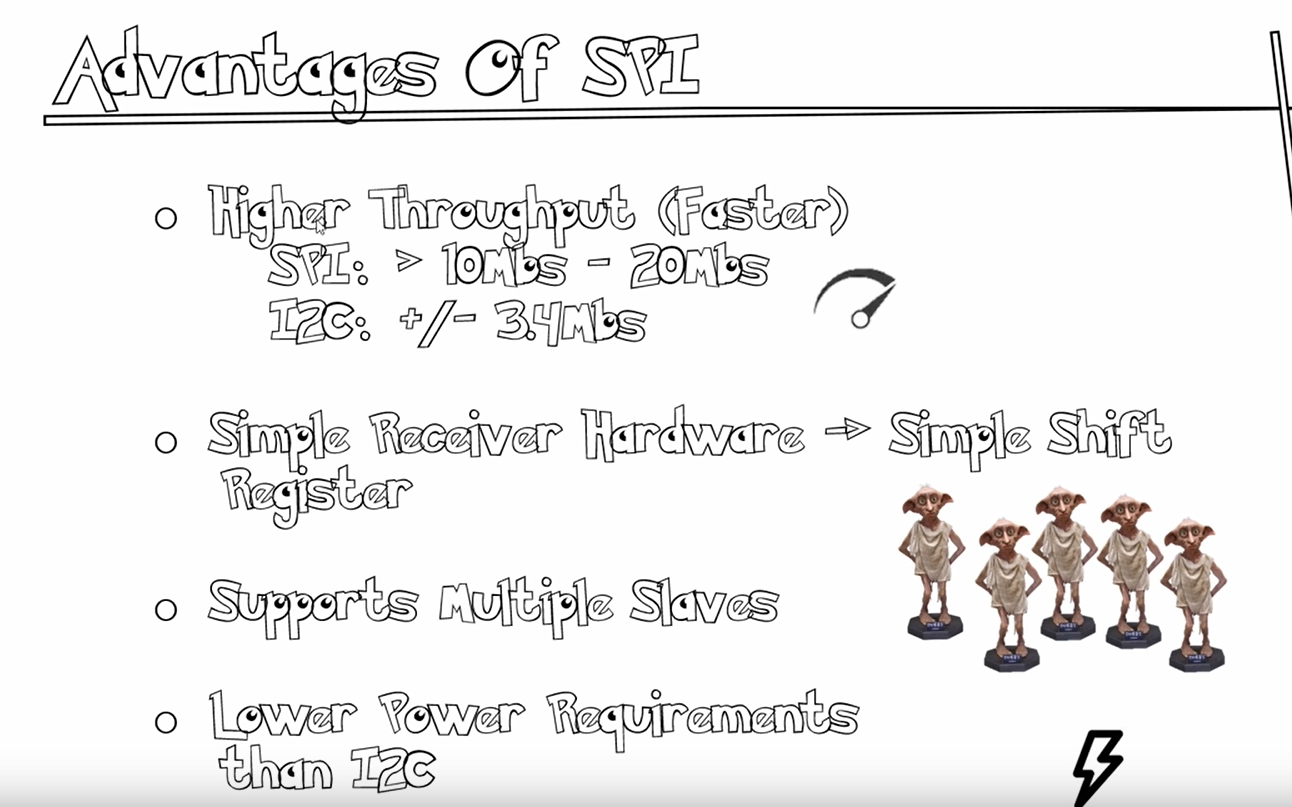

spi interface

Serial Peripheral Interface (SPI) is a synchronous serial communication interface specification used for short-distance communication, primarily in embedded systems.

https://en.wikipedia.org/wiki/Serial_Peripheral_Interface

https://www.youtube.com/watch?v=ba0SQwjTQfw

https://www.youtube.com/watch?v=AuhFr88mjt0