Some notes about Queued Invalidation in VT-d

本文将介绍VT-d中Queued Invalidation的相关知识点。

Queued Invalidation的详细内容请参考VT-d spc的6.5.2节。

概念

spec中的描述如下:

The queued invalidation provides an advanced interface for software to submit invalidation requests to hardware and to synchronize invalidation completions with hardware.

usage

The queued invalidation interface uses IQ(Invalidation Queue), which is a circular buffer in system memory. Software submits commands by writing Invalidation Descriptors to the IQ.

dmar_issue_qi_request是研究Queued Invalidation的入口函数。

从源码中可以看到,acrn在invalid dmar context cache, invalid dmar iotlb, invalid dmar interrupt entry cache时,会使用到Queued Invalidation。

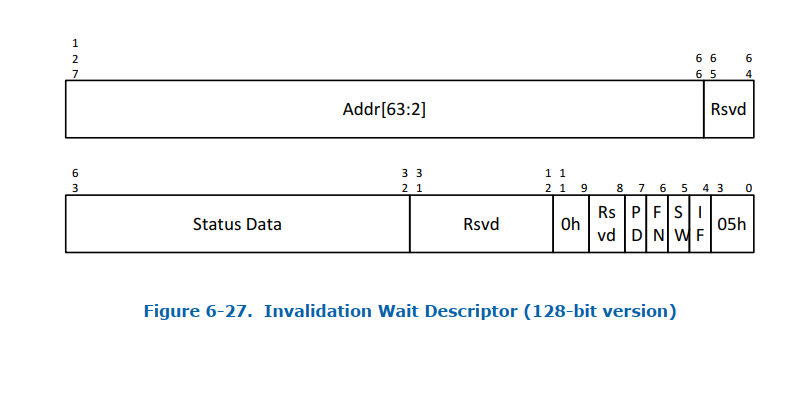

acrn向QI中submit 一个Invalidation Descriptor时,紧接着会submit Invalidation Wait Descriptor(VT-d spec 6.5.2.8)。

1 | invalidate_desc_ptr->hi_64 = hva2hpa(&qi_status); |

将&qi_status写入Addr,将DMAR_INV_STATUS_COMPLETED写入Status Data(见上图),这意味着:当硬件处理完invalidation requests 时,会将qi_status的值赋值为DMAR_INV_STATUS_COMPLETED。

软件先将qi_status赋值为DMAR_INV_STATUS_INCOMPLETE,然后loop,直至硬件将qi_status的值赋值为DMAR_INV_STATUS_COMPLETED。

details

Since information from the context-cache may be used to tag entries in the PASID-cache, IOTLB and paging-structure caches, software must always follow a context-cache invalidation with a PASID cache invalidation (if context-cache entry supports requests-with-PASID, or if Scalable Mode Translation is enabled), followed by an IOTLB invalidation.

context-cache invalidation and IOTLB invalidation has dependency relationship.