Notes about PCI Express Configuration Space

本文将记录PCI Express Configuration Space相关笔记。

1. Background

The PCI Express bus extends the Configuration Space from 256 bytes to 4096 bytes. This extended configuration space cannot be accessed using the legacy PCI method (through ports 0xCF8 and 0xCFC).

In the beginning there was a configuration space, for each PCI device function, of 256 bytes.

This space was accessed using the PCI legacy mechanism (we can ignore the fact there were two mechanisms) at ports 0xcf8 and 0xcfc.

The PCIe extended this space from 256 bytes to 4KiB and introduced a new mechanism to access the configuration space (all of it).

So, to recap:

- There is a single PCI configuration space of 4KiB. It is divided into a PCI 3.0 Compatible region (from 0x000 to 0x0ff) and PCIe extended configuration region (from 0x100 to 0xfff).

- There are two mechanism to access the PCI configuration space. One is the legacy mechanism at 0xcf8/0xcfc the other one is a memory mapped area.

- The Legacy mechanism can only access the compatibility region (the first 256 bytes).

- The ECAM can access all of the space.

2. ECAM

Enhanced Configuration Access Mechanism (ECAM)

PCI Express extends the Configuration Space to 4096 bytes per Function as compared to 256 bytes allowed by PCI Local Bus Specification.

PCI Express Configuration Space is divided into a PCI 3.0 compatible region, which consists of the first 256 bytes of a Function’s Configuration Space, and a PCI Express Extended Configuration Space which consists of the remaining Configuration Space .

The PCI 3.0 compatible Configuration Space can be accessed using either the mechanism defined in the PCI Local Bus Specification or the PCI Express Enhanced Configuration Access Mechanism (ECAM).

Accesses made using either access mechanism are equivalent. The PCI Express Extended Configuration Space can only be accessed by using the ECAM.

The base address of the MMIO area for the configuration space of each PCIe devices in a PCI segment group is given in the ACPI table MCFG.

The MCFG table lists, for each PCI segment group, the first and last (inclusive) bus number of the PCI segment group and the base address of the PCI Express enhanced configuration space.

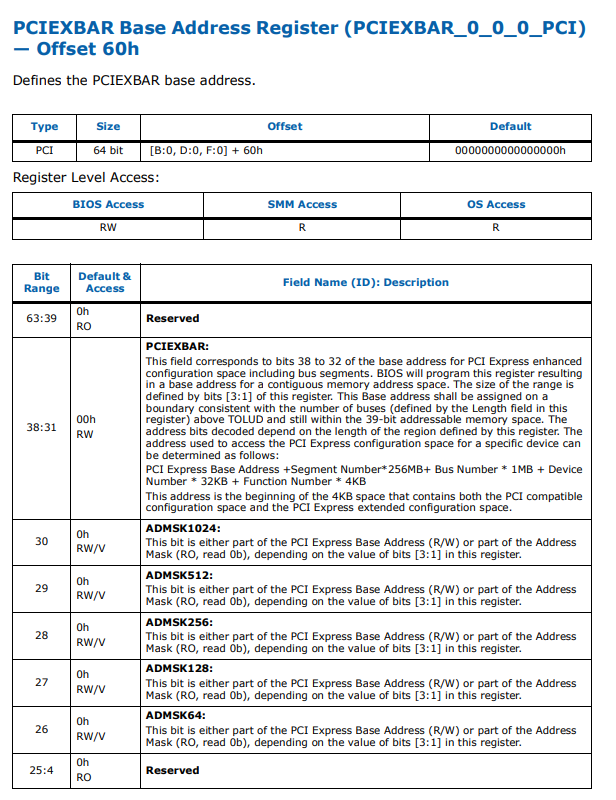

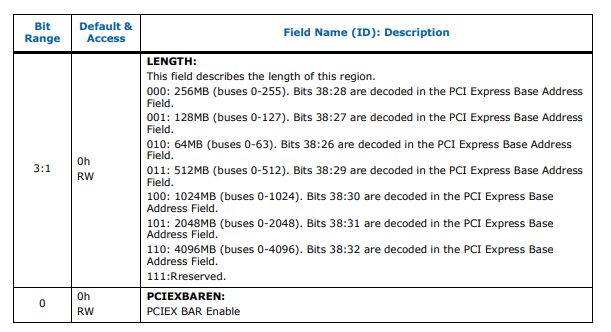

The MCFG table is setup by the BIOS/UEFI based upon the value of the PCIEXBAR (offset 60h) in the Host Bridge PCI configuration space.

3. Verification

1 | $ lspci -xxx -s 00:0.0 |

1 | $ cat /proc/iomem | grep MMCONFIG |

参考资料: