Introduction to Compute Express Link (CXL)

本文将介绍Compute Express Link (CXL)相关知识点。

1. Definition

Compute Express Link™ (CXL™) is an industry-supported Cache-Coherent Interconnect for Processors, Memory Expansion and Accelerators. CXL technology maintains memory coherency between the CPU memory space and memory on attached devices, which allows resource sharing for higher performance, reduced software stack complexity, and lower overall system cost. This permits users to simply focus on target workloads as opposed to the redundant memory management hardware in their accelerators.

CXL is designed to be an industry open standard interface for high-speed communications, as accelerators are increasingly used to complement CPUs in support of emerging applications such as Artificial Intelligence and Machine Learning.

2. Motivation

通俗地说,有了CXL,Host在访问Device Memory时,可以得到像访问本地Memory一样的体验;同样的,Device访问host Memory时,也像是在访问Device Memory一样。

我们已经有了PCIe这样的高速串行总线,为什么还要再搞出一个新的CXL呢 ?主要是因为PCIe不支持cache的一致性,这会导致每次Device去访问Host上的内存时,即便已经访问了多次而且内存也没有变化的情况下,都要重新访问,这样导致性能很差。另外因为人工智能和机器学习的兴起,FPGA/GPU 卡上会有大量的内存,在不进行运算时闲置的话,会造成资源浪费。而因为PCIe不支持Cache的一致性,Host访问设备上的内存也会非常的慢(CPU访问设备的内存是不cache的,意味着这次访问完而且设备内存也没有变化的情况下,下次还要重新访问。为什么不cache 呢?因为设备的内存不能汇报自己的改变)。所以Intel就发明了CXL,它在PCIe的基础上加入了Cache一致性的支持以用来提高设备和主机之间内存互相访问的速度。

3. Components

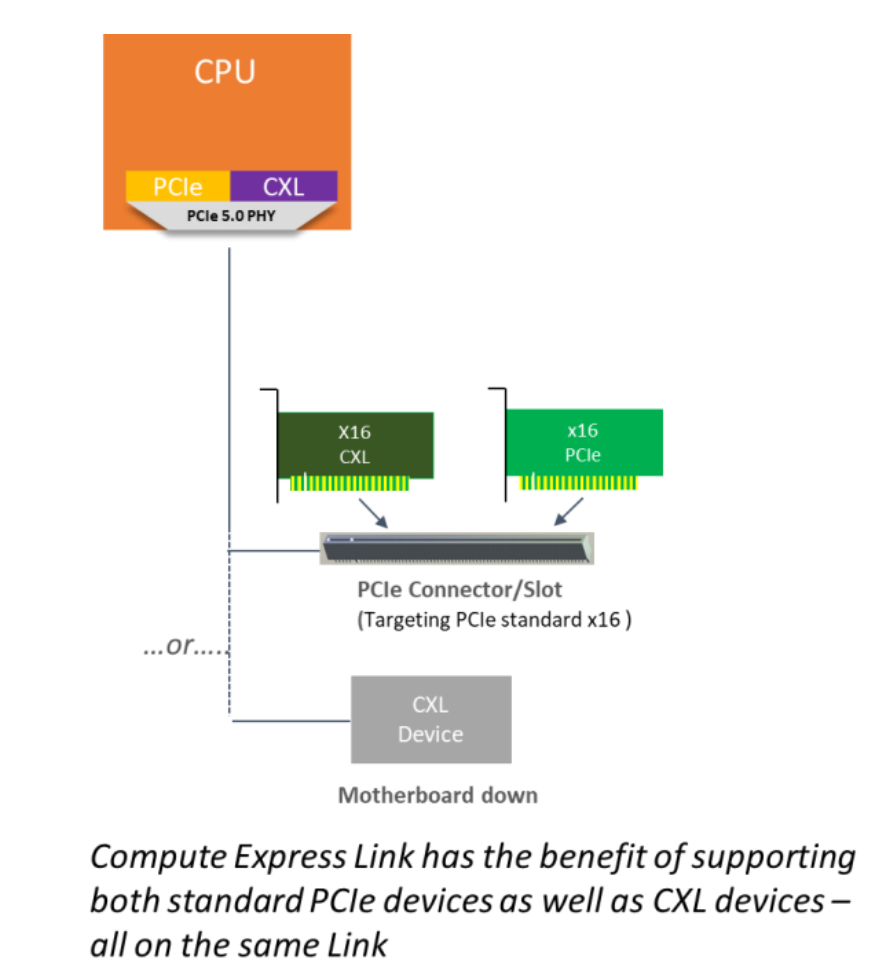

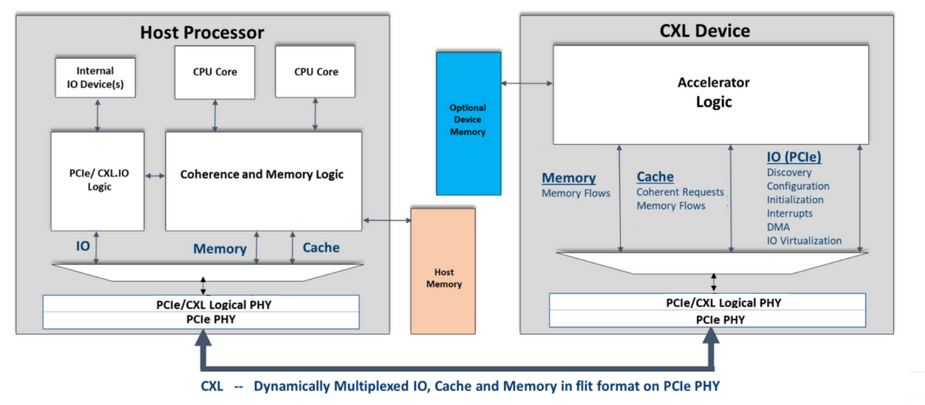

CXL在PCIe 5.0的基础上复用三种类型的协议:

- CXL.io: Provides discovery, configuration, register access, interrupts, etc.

- CXL.cache: Provides the CXL device access to the processor memory

- CXL.memory: Provides the Processor access to the CXL device attached memory

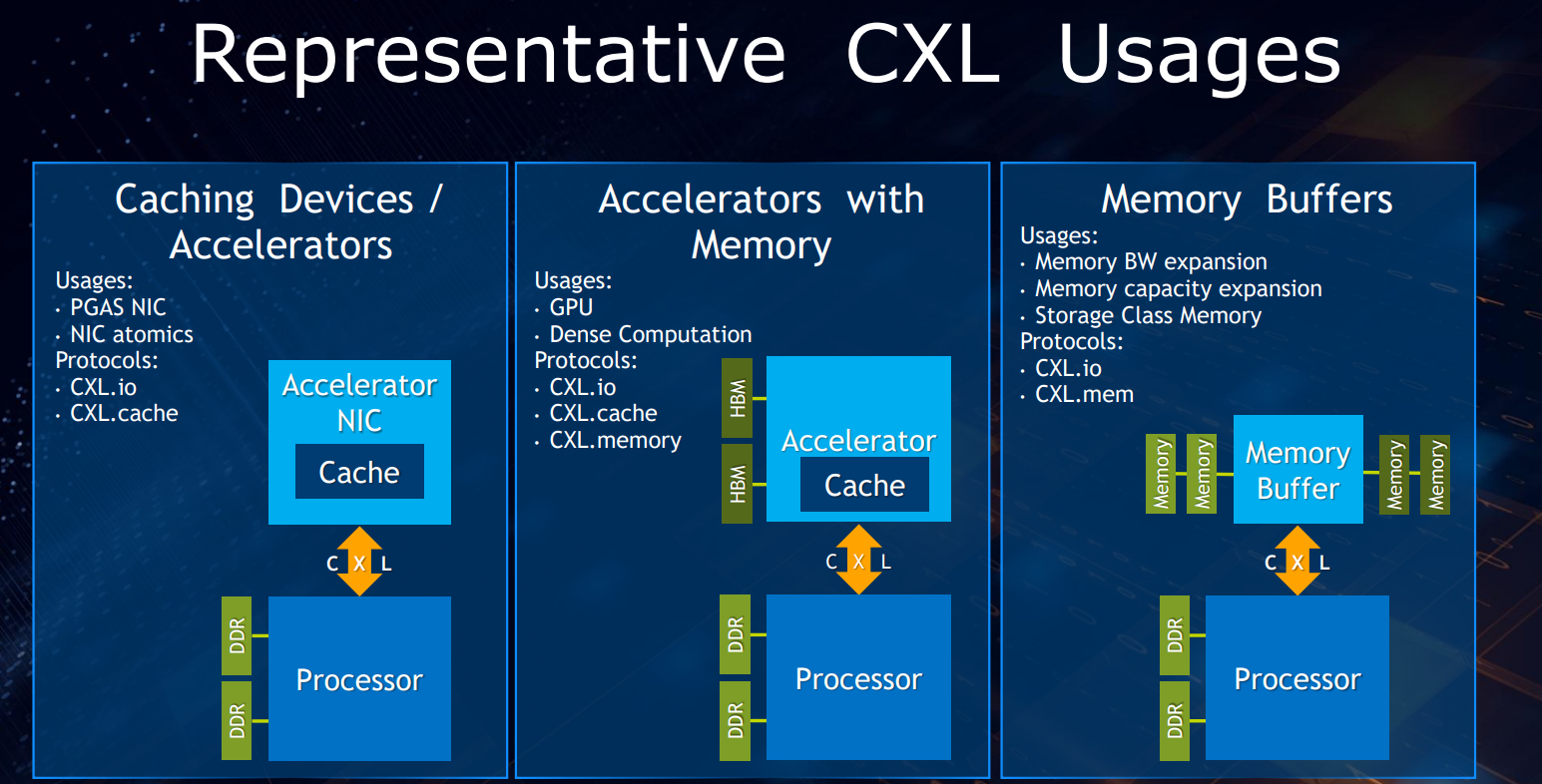

Each of these are illustrated in the block below.

4. Usage

HBM(High Bandwidth Memory)

5. Summary

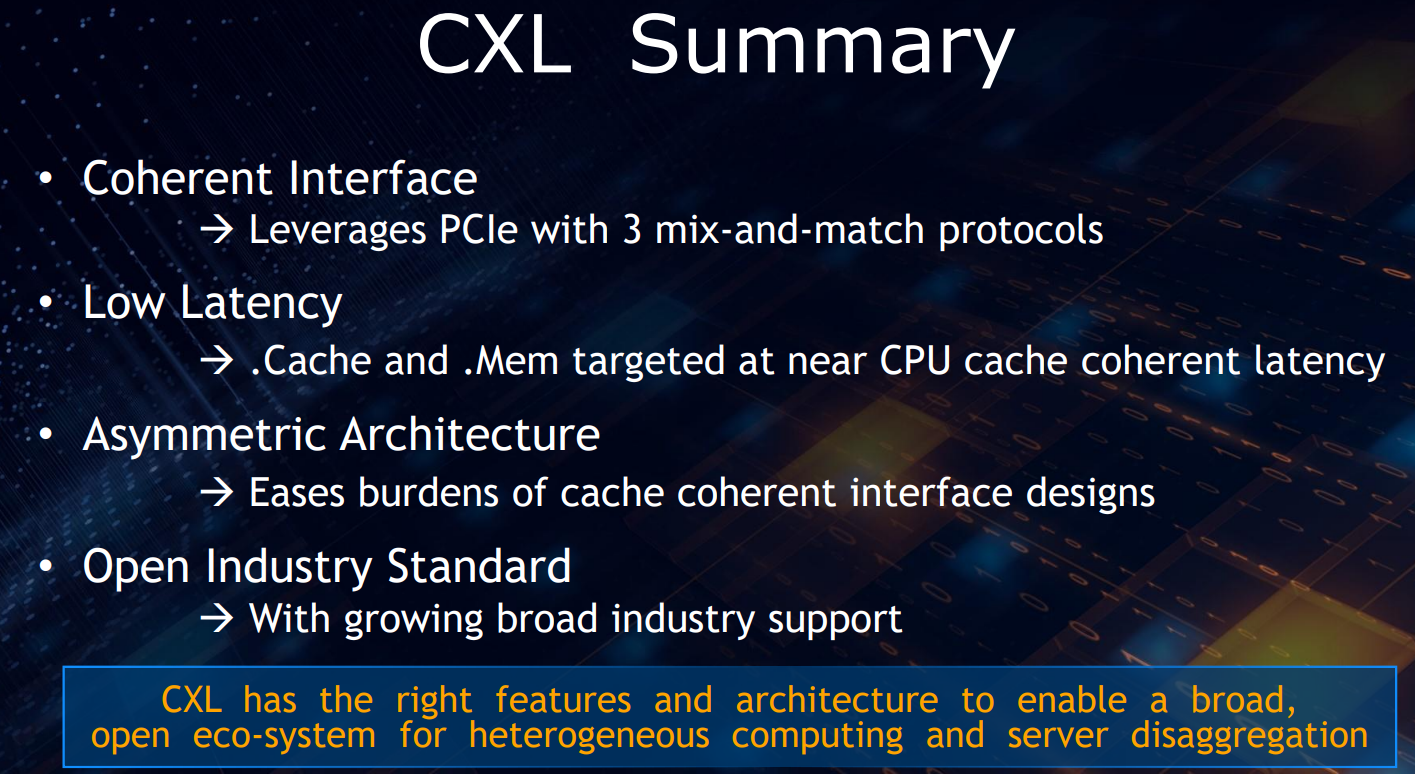

In short, CXL is an open industry standard interconnect offering high-bandwidth, low-latency connectivity between the host processor and devices including accelerators, memory expansion, and smart I/O devices. CXL utilizes the PCI Express® (PCIe®) 5.0 physical layer infrastructure and the PCIe alternate protocol to address the demanding needs of high-performance computational workloads in Artificial Intelligence, Machine Learning, communication systems, and HPC through the enablement of coherency and memory semantics across heterogeneous processing and memory systems.

参考资料: