Introduction to PCIe Page Request Interface

本文将记录PCIe中PRI(Page Request Interface)相关知识点。

阅读本文前,读者需要对ATS和guest memory pinning when direct assignment of I/O devices有一定的了解。

PRI(Page Request Interface) allows functions(BDF中的F) to raise page faults to the IOMMU.

1. DMA Page Fault Support

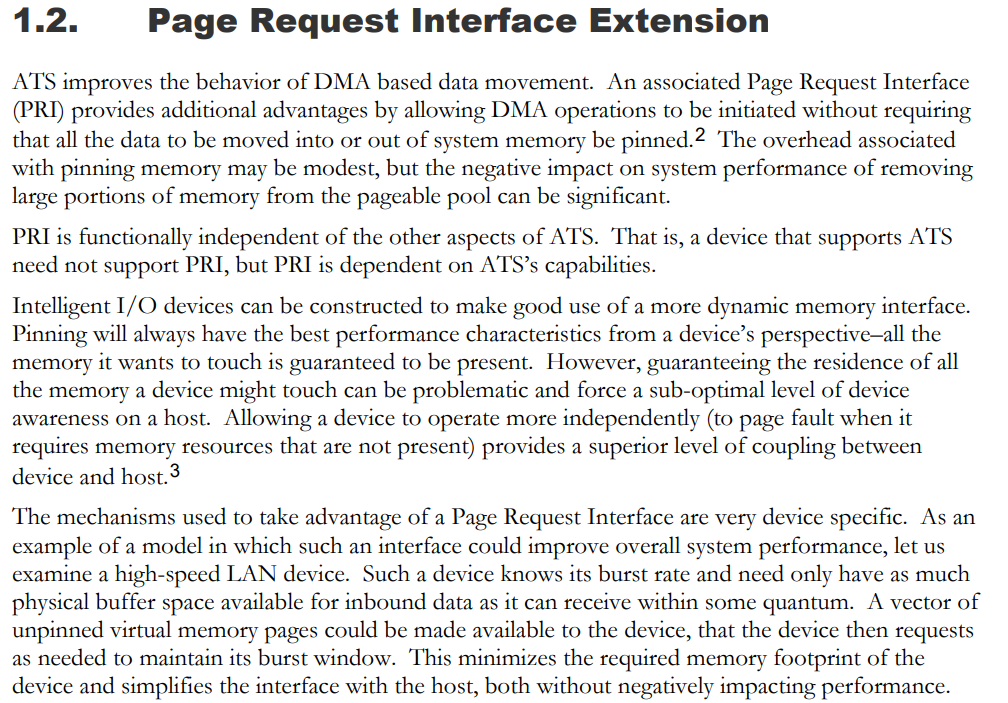

Description from PCIe spec:

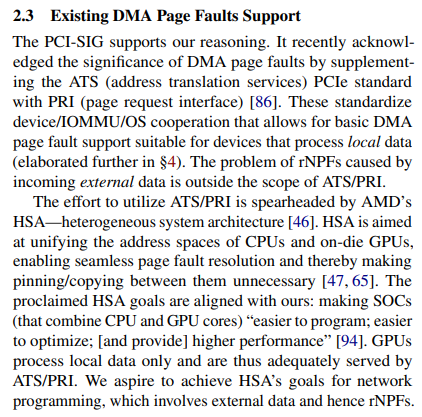

Description from ASPLOS ’17 paper:

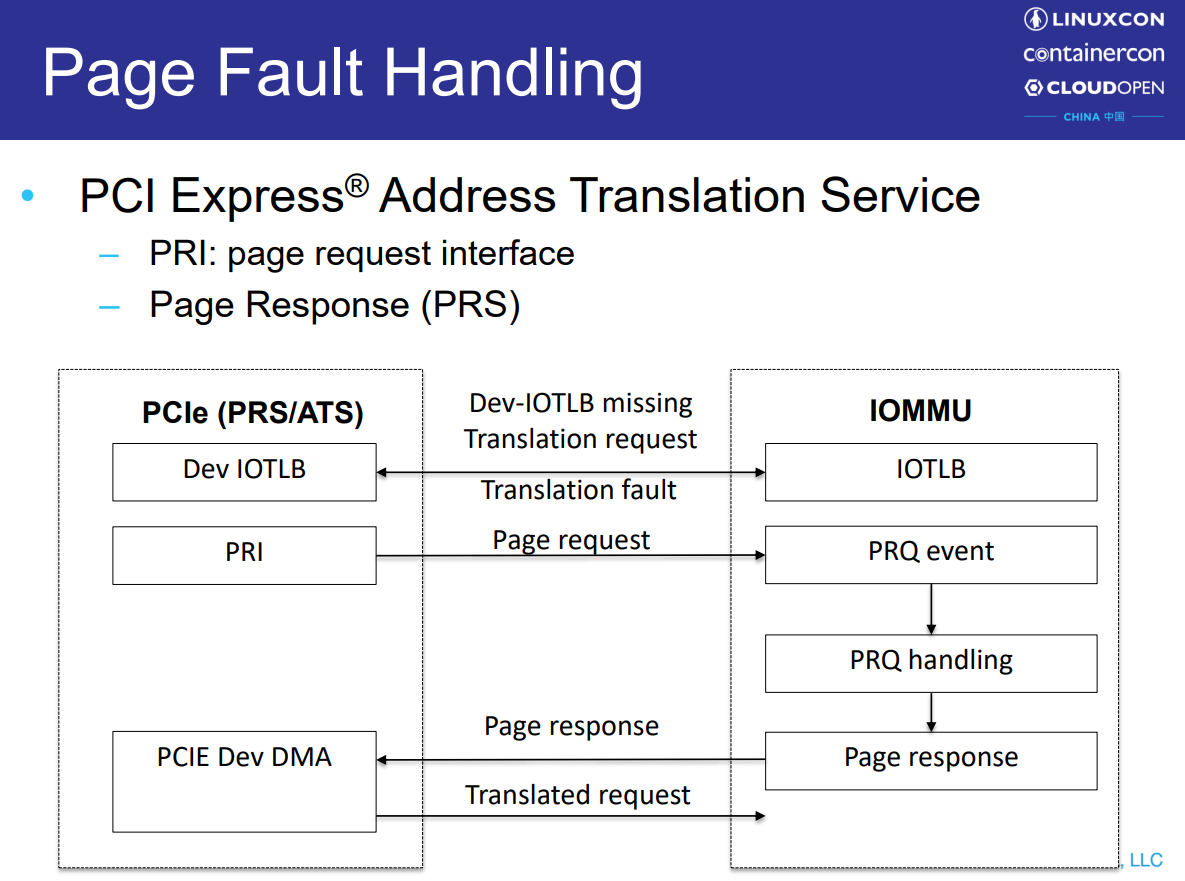

2. Page Request Services

The general model for a page request is as follows:

- A Function determines that it requires access to a page for which an ATS translation is not available.

- The Function causes the associated Page Request Interface to send a Page Request Message to its RC. A Page Request Message contains a page address and a Page Request Group (PRG) index. The PRG index is used to identify the transaction and is used to match requests with responses.

- When the RC determines its response to the request (which will typically be to make the requested page resident), it sends a PRG Response Message back to the requesting Function.

- The Function can then employ ATS to request a translation for the requested page(s).

3. Implementation

4. Q & A

Q: 如果IOMMU支持pri的话,设备也需要去适配pri才能work吗?

A: 是的,设备要支持ats和pri,并且提供device tlb

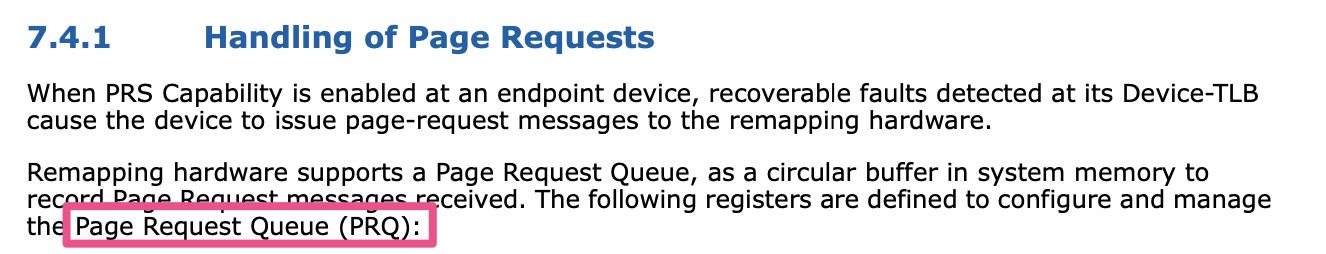

Q: 请问是设备往PRQ中填写的io page fault的entry吗?

A: 是的,PRQ就是一个共享内存

Q: 每个设备一个PRQ吗?

A: 不是,一个iommu只有一个PRQ,不同设备都往里面放

Q: 那如果两个设备同时往PRQ中放的话,会存在竞态吗?

A: 不会,iommu硬件分发的,保序的

Q: 就是如果两个设备同时往PRQ写入entry的话,iommu也做仲裁,所以可以解决竞态的问题?

A: 是的,不过设备无法写PRQ entry,只有iommu可以写,设备发page request pci message

Q: 最后是iommu发中断通知os来处理这些io page fault吧?

A: 是的

参考资料:

- Address Translation Services Revision 1.1

- Shared Virtual Memory in KVM

- Page Fault Support for Network Controllers, ASPLOS ’17