Notes about Intel CET

本文将mark下Intel CET(Control-flow Enforcement Technology)的相关notes,主要内容转载自Intel CET 安全防御机制深度解析。

概述

CET(Control-flow Enforcement Technology)机制是 Intel提出基于硬件的⽤于缓解 ROP/JOP/COP的新技术。特别强调下,他是基于硬件⽀持的解决⽅案。从Intel的Tigerlake (11th gen),Alderlake (12th gen)/Sapphire-Rapid起,粗颗粒度地旨在预防前向( call/jmp )和后向( ret )控制流指令劫持来御防ROP的攻击。因此针对防御对象不同,CET技术又分为CET-SS用于针对ROP的ret指令和CET-IBT用于针对JOP/COP的jmp/call指令。

CET为何而生

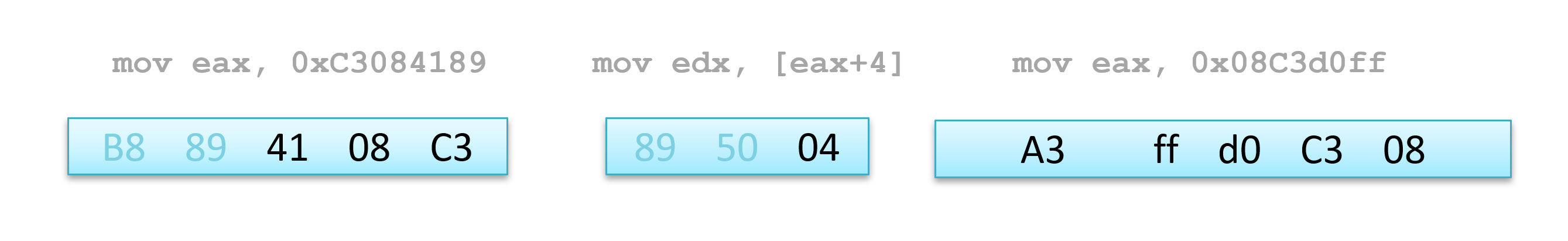

说到防御者CET,就不得不提他的进攻者ROP了。什么是ROP? 来看⼀个例⼦,假设程序中正常执行如下代码⽚段,注意此时其中不含ret或call指令。

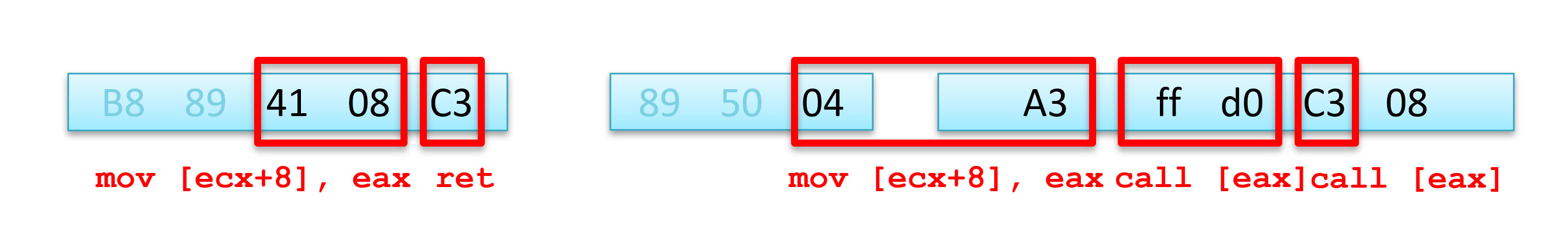

但是,如果稍加偏移⼀下解释代码的地址时,就会导致出现完全不⼀样的指令,如下图所示:

如果按照红框中的顺序解释这些指令的时候,那么将会产⽣⾮代码预期的结果,会出现原代码中未出现过的 ret 指令以及 call 指令,这些指令序列被称为 gadget 。通过仔细构造这些由ret指令终⽌的指令集,攻击者可以执⾏原程序中⾮预期的任意恶意代码,这种新产生ret攻击被称为 ROP 攻击,同理还有COP/JOP(call/jmp)攻击。

为了防御这种此类ROP攻击,Intel在硬件机制上推出了CET缓解机制,针对不同的攻击行为分为CET-SS(影子栈)和CET-IBT(间接跳转跟踪)。

#CP异常

CET-SS和CET-IBT 在实现机制上属于CPU内部异常。当执行启动CET发现执行执行流中没有endbr64或函数返回ret和影子栈中shandow stack保存的ret不一致时,CPU内部出发异常,这里CET占用的中断向量21号,触发#CP并归为陷阱执行中断处理程序exc_control_protection(),对CET-SS CET-IBT分情况进行报错。CET-IBT -> “traps: Missing ENDBR: xxx”, CET-SS-> #CP(control protect)。

CET-SS(Shadow Stack)

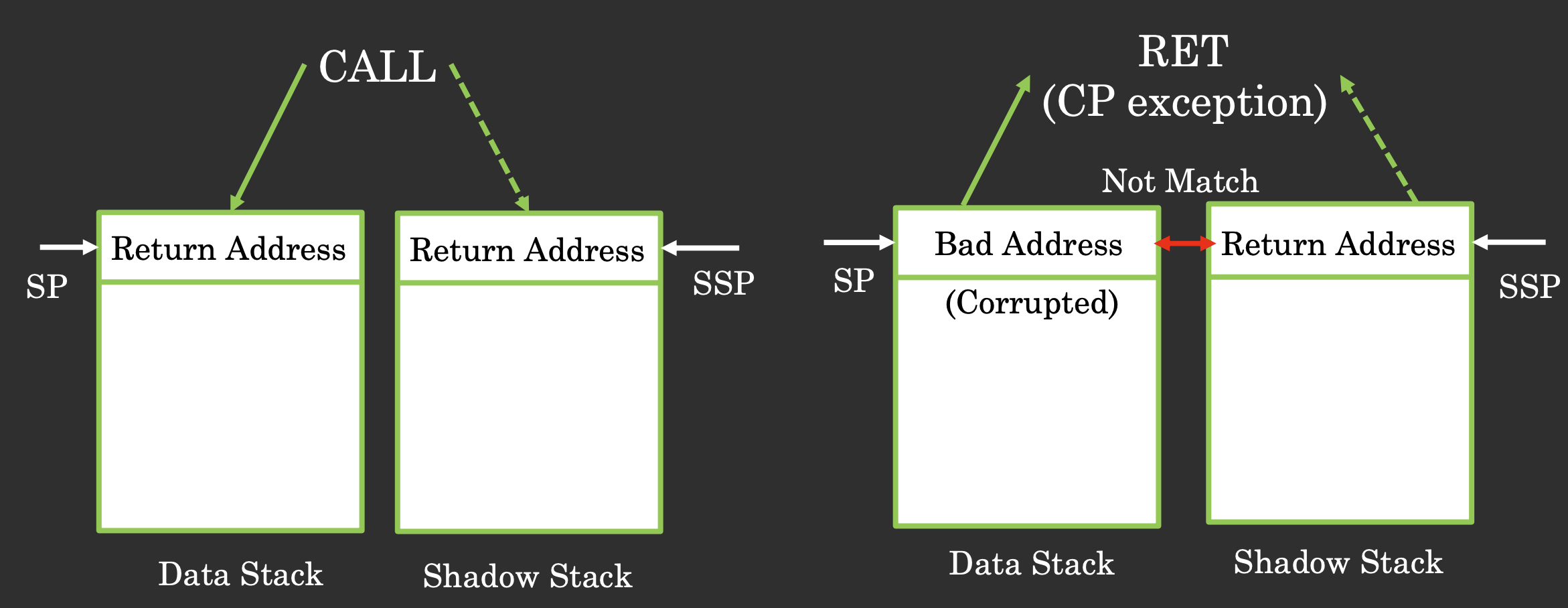

Intel 提出了⼀种基于硬件的 CET 解决⽅案,其中之⼀的 shadow stack 机制⽤于缓解 ROP 攻击。ROP 依赖于 ret 指令,其中要执⾏的后续指令地址从堆栈中获得。因此 ROP 攻击的前提是攻击者能够在堆栈中构造数据。那么再来看 shadow stack 机制是怎么⼯作的。

CET 使操作系统能够创建⼀个 shadow stack (影⼦栈)。正常情况下,当执⾏ call 指令时,会将 call 指令后⼀条指令地址压栈。当启⽤了 shadow stack 后,会同时在普通数据栈和 shadow stack 中压⼊返回地址,随后在执⾏ ret 返回时,会将 shadow stack 中的返回地址和普通数据栈中的返回地址做对⽐,如匹配,则正常执⾏,如不匹配,则触发#CP(Controlflow Protection) 异常。如下图所示:

CET-IBT(Indirect Branch Tracking)

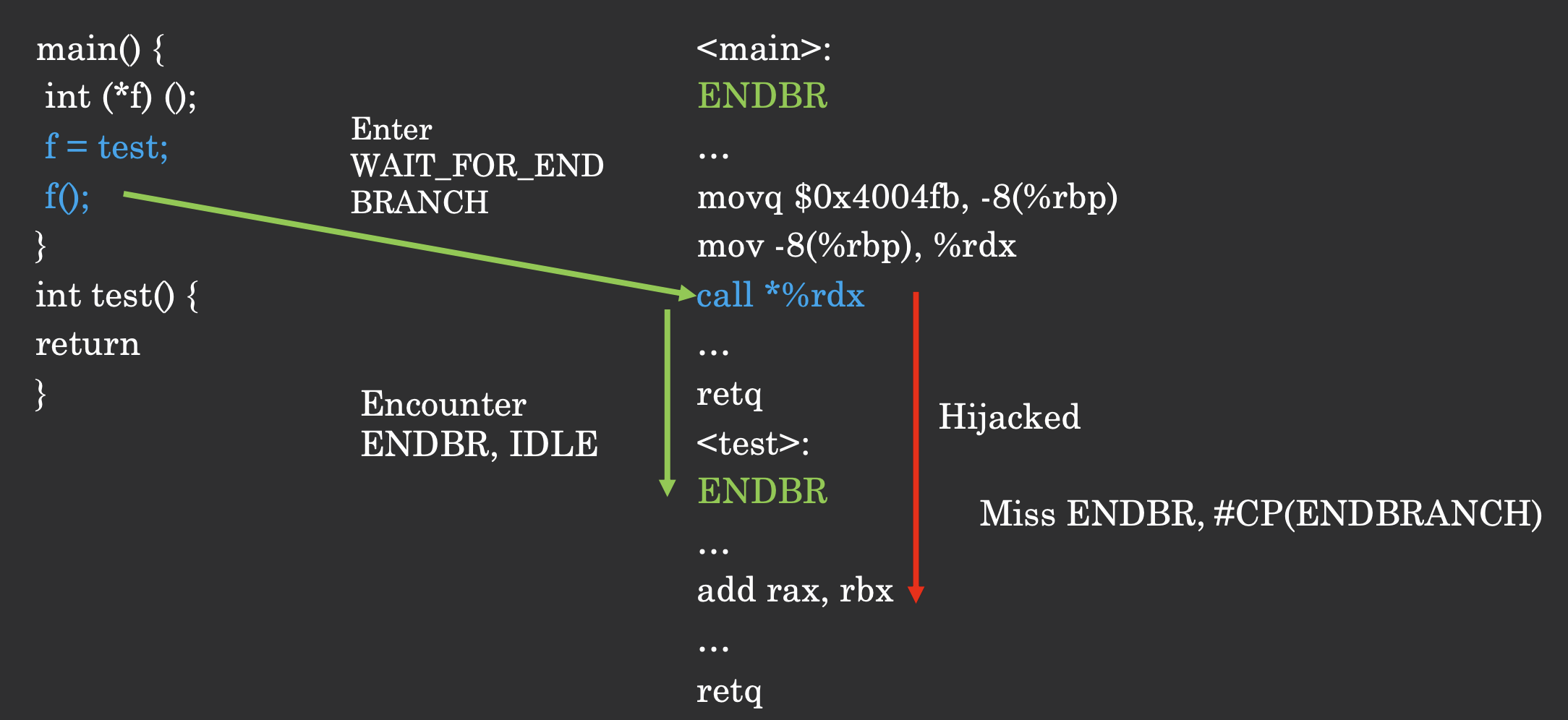

JOP/COP 攻击⼿法与 ROP 类似,只不过是把 ROP 中以 ret 指令做跳板的关键点替换成了 call/jmp 指令。这种不需要 ret 指令的攻击场景下,前⾯所说的 shadow stack 机制就失效了。这种情况下, CET 的第⼆种机制 IBT(Indirect Branch Tracking) 就应运⽽⽣了。

IBT(Indirect Branch Tracking),间接跳转跟踪”希望能防止攻击者让间接跳转(例如,通过指针变量进行的函数调用)进入一个不应该走到的地方。

IBT 是为了防御面向跳转编程的(jump-oriented programming);工作原理是试图确保每个 indirect branch 的目标确实都是适合作为跳转目标的。IBT 的方法有很多,每一种都有自己的优势和劣势。例如,内核在 5.13 开发周期中支持了编译器实现的 IBT 机制。在这种模式下,编译器通过一个 “jump table, 跳转表” 来完成每一个间接跳转,不仅确保目标是要供间接跳转使用的,而且要确保被调用函数的原型与调用者所期望的一致。这种方法是很有效的,但要增加很多编译、运行时的开销。

CET-IBT方法相当简单,但优点是得到了硬件的支持,因此速度更快.如果 IBT 被启用,那么 CPU 将确保每个间接跳转都落在一条特殊指令(endbr32 或 endbr64)上,该指令执行时跟 no-op 效果一致。如果发现意外,那么处理器将引发一次 control-protection(#CP)exception。

参考资料:

- deepseek[介绍下Intel CET技术]

- Intel CET 安全防御机制深度解析

- Limitations and Opportunities of Modern Hardware Isolation Mechanisms

- A Technical Look at Intel’s Control-flow Enforcement Technology

- How to Survive the Hardware-assisted Controlflow Integrity Enforcement

- CETIS: Retrofitting Intel CET for Generic and Efficient Intra-process Memory Isolation

- Control-flow Enforcement Technology