Accelerating Two-Dimensional Page Walks for Virtualized Systems

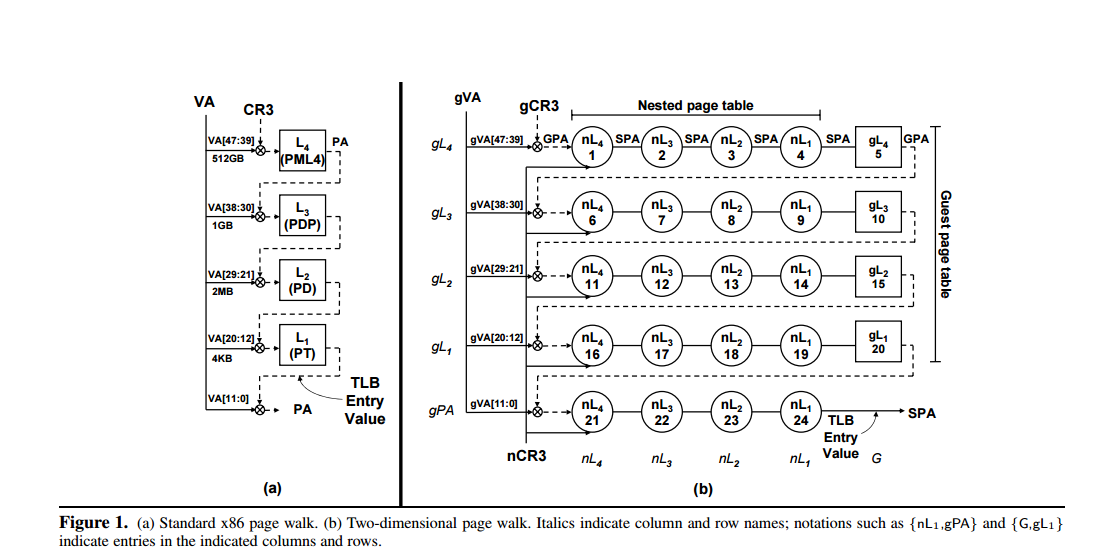

文章目录

Accelerating Two-Dimensional Page Walks for Virtualized Systems

此论文是ASPLOS’08上的一篇文章,今天特意总结一下,希望对读者会有所帮助。

相关资料

| 姓名 | 主页 | dblp |

|---|---|---|

| Ravi Bhargava | Ravi Bhargava | Ravi Bhargava |

介绍

本文介绍了在虚拟化环境中,AMD的2D page walk工作负载,以及如何利用page walk cache来降低负载。本文最大的亮点在于背景知识,详细清晰地讲述了虚拟化环境下地址的映射过程。

贡献点:

这项工作是第一次讨论AMD皓龙page walk cache(PWC)。 PWC旨在通过将页面entry存储在小型快速缓存中来减少native页面访问的延迟,以避免内存层次结构访问。

将PWC扩展到nested paging上,同时,结合Nested TLB可以提高虚拟机的性能。

大页的引入可以降低2D page walk的开销。

背景

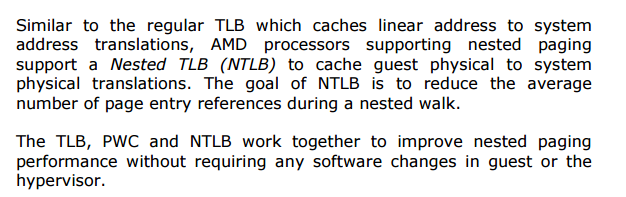

x86 Native 页面映射

虚拟化内存管理

2D page table walk

好好阅读!

大页

the TLB must consider the page size for a given translation to be the smaller of the nested and guest page sizes

page walk加速

Native page walk PWC

2-D page walk PWC

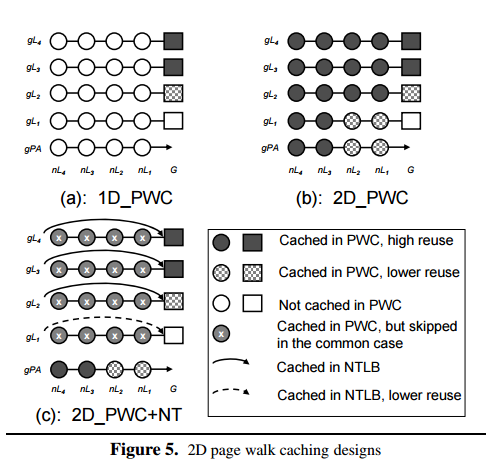

One-Dimensional PWC

Two-Dimensional PWC

Two-Dimensional PWC with Nested Translations

NTLB是映射客户机物理地址到主机物理地址的entry,它和TLB是独立的。