中断基本概念的建立

中断从设备发送到CPU需要“可编程中断控制器”的转发(MSI除外)。中断控制器发展至今,经历了PIC和APIC两个阶段。

1. PIC

也就是8259A芯片。PIC的相关介绍参见系统虚拟化2.4.1章节。

明白PIC中重要的寄存器以及PIC向CPU递交中断的流程即可。若想深究,可以参见8259A Programmable Interrupt Controller

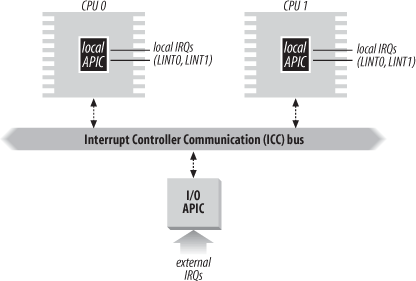

2. APIC

PIC可以在UP(单处理器)平台上工作,但无法用于MP(多处理器)平台。为此,APIC应运而生。

APIC的相关介绍参见系统虚拟化2.4.1章节。

APIC的发展历程:

APIC->xAPIC->x2APIC

LAPIC处理的中断类型有如下三种:

- Local interrupt - configured by local vector table(LVT)

- External interrupt - from IOAPIC/MSI

- inter-processor interrupt(IPI) - configured by interrupt command register(ICR)

详细内容请参见SDM(ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER)部分。

3. MSI

3.1 What are MSIs?

A Message Signaled Interrupt is a write from the device to a special address which causes an interrupt to be received by the CPU.

The MSI capability was first specified in PCI 2.2 and was later enhanced in PCI 3.0 to allow each interrupt to be masked individually. The MSI-X capability was also introduced with PCI 3.0. It supports more interrupts per device than MSI and allows interrupts to be independently configured.

3.2 Why use MSIs?

There are three reasons why using MSIs can give an advantage over traditional pin-based interrupts.

Pin-based PCI interrupts are often shared amongst several devices. To support this, the kernel must call each interrupt handler associated with an interrupt, which leads to reduced performance for the system as a whole. MSIs are never shared, so this problem cannot arise. for detail

When a device writes data to memory, then raises a pin-based interrupt, it is possible that the interrupt may arrive before all the data has arrived in memory (this becomes more likely with devices behind PCI-PCI bridges). In order to ensure that all the data has arrived in memory, the interrupt handler must read a register on the device which raised the interrupt. PCI transaction ordering rules require that all the data arrive in memory before the value may be returned from the register. Using MSIs avoids this problem as the interrupt-generating write cannot pass the data writes, so by the time the interrupt is raised, the driver knows that all the data has arrived in memory.

PCI devices can only support a single pin-based interrupt per function. Often drivers have to query the device to find out what event has occurred, slowing down interrupt handling for the common case. With MSIs, a device can support more interrupts, allowing each interrupt to be specialised to a different purpose.

3.3 misc

intel系统中,MSI允许PCI设备直接发送中断到LAPIC,不需要通过IOAPIC。

MSI allows the device to write a small amount of interrupt-describing data to a special memory-mapped I/O address, and the chipset then delivers the corresponding interrupt to a processor.

A common misconception with MSI is that it allows the device to send data to a processor as part of the interrupt. The data that is sent as part of the memory write transaction is used by the chipset to determine which interrupt to trigger on which processor; that data is not available for the device to communicate additional information to the interrupt handler.

On Intel systems, the LAPIC must be enabled for the PCI (and PCI Express) MSI/MSI-X to work, even on uniprocessor (single core) systems. In these systems, MSIs are handled by writing the interrupt vector directly into the LAPIC of the processor/core that needs to service the interrupt.

详细内容请参见SDM(MESSAGE SIGNALLED INTERRUPTS)部分。

参考资料: